Содержание

Шина данных. разрядность шины — Информатика, информационные технологии

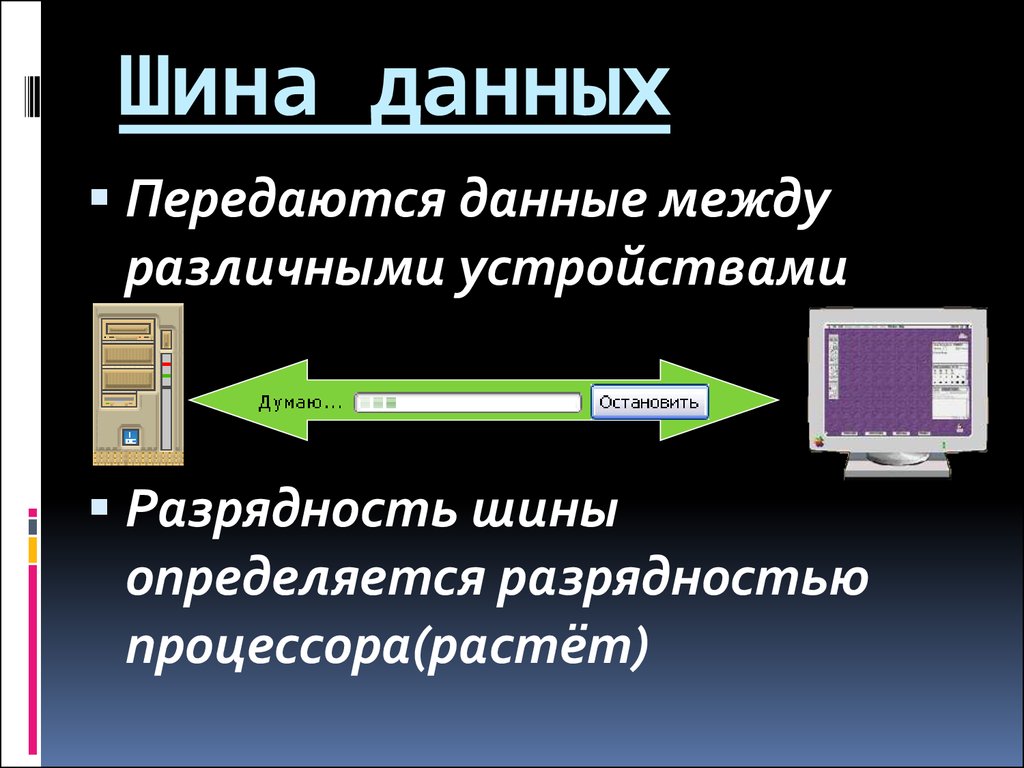

Шину данных образуют линии, служащие для передачи данных между отдельными структурными группами ПК. Исходным пунктом линий данных является центральный процессор. Он определяет разрядность шины данных, т.е. число линий, по которым передаются данные. Чем выше разрядность шины данных, тем больший объем данных можно передать по ней за некоторый определенный промежуток времени и тем выше быстродействие компьютера.

В первых ПК использовался процессор Intel 8088. Этот 16-разрядный процессор имел всего лишь 8 внешних линий данных (этим объясняется его низкая стоимость). Для внутренних операций было задействовано 16 линий данных, благодаря чему процессор мог одновременно обрабатывать два восьмиразрядных числа. Но на внешнем уровне к нему присоединялась дешевая восьмиразрядная шина данных. Эти 8 линий обеспечивали связь со всеми микросхемами на системной плате, выполняющими функции обработки данных, и всеми платами расширения, установленными в гнездах. Таким образом осуществлялась передача данных между платами расширения и процессором.

Таким образом осуществлялась передача данных между платами расширения и процессором.

Современные процессоры допускают внешнее подключение большего числа линий данных: процессор 80286 — 16 линий данных, процессоры 80386 DX и 80486 DX — 32 линии, а процессор Pentium — 64 линии данных.

Адресная шина. Разрядность шины

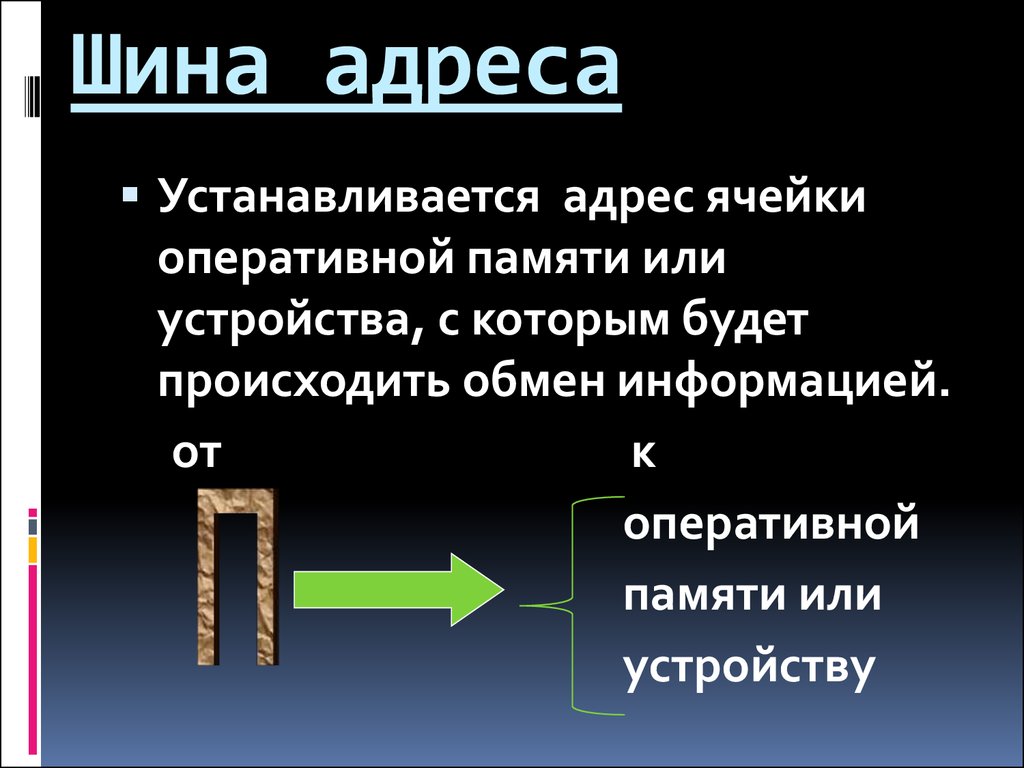

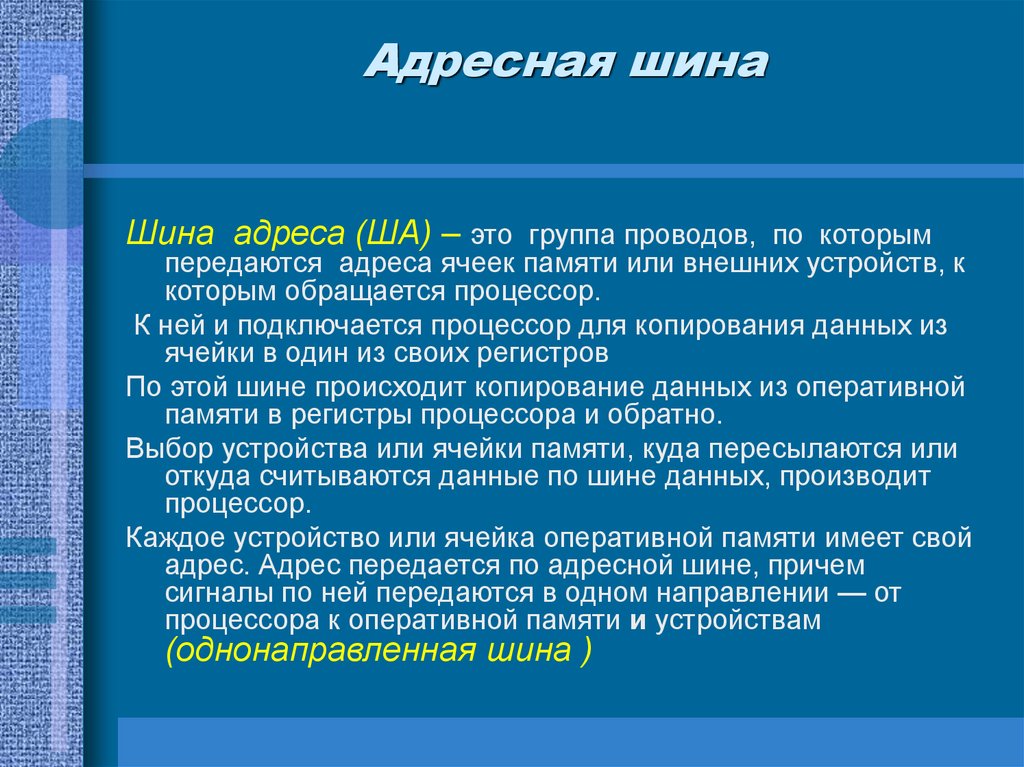

Другая группа линий образует адресную шину. Эта шина используется для адресации. Каждая ячейка памяти и устройство ввода-вывода компьютера имеет свой собственный адрес.

При считывании или записи данных процессор должен сообщать, по какому адресу он желает прочитать или записать данные, для чего необходимо указать этот адрес.

В отличие от шины данных шина адреса является однонаправленной.

Разрядность адресной шины определяет максимальное число адресов, по которым может обратиться процессор, т. е. число линий в адресной шине показывает, каким объемом памяти может управлять процессор. Учитывая, что одна адресная линия обеспечивает представление одного разряда двоичного числа, формулу для максимального объема адресуемой памяти можно записать в следующем виде:

максимальное число адресов = 2n,

где n — разрядность адресной шины.

Процессор 8088 имел 20 адресных линий, что в соответствии с приведенной формулой обеспечивало адресацию памяти объемом:

220 =1 048 576 байт = 1024 Кбайт = 1 Мбайт.

Это тот самый предельный объем памяти, который все еще имеет силу в операционной системе DOS.

Совсем иная ситуация с процессором 80286. Он имеет 24 адресных линии и поэтому в состоянии управлять памятью объемом:

224= 16 777 216 байт =16 Мбайт.

Для обеспечения связи с микросхемами памяти число адресных линий процессора должно равняться числу адресных линий на системной плате.

Процессоры 80386, 80486 и Pentium имеют 32 адресных линии, что обеспечивает адресацию свыше 4 млрд. ячеек памяти. На системной плате с такими процессорами должно быть 32 линии, обеспечивающие обмен адресами между центральным процессором и всеми важными периферийными микросхемами.

Шина управления

Линии шины управления на системной плате служат для управления различными компонентами ПК. По выполняемой ими функции их можно сравнить с переводной стрелкой на железнодорожных путях.

По выполняемой ими функции их можно сравнить с переводной стрелкой на железнодорожных путях.

С помощью небольшого числа линий шина управления обеспечивает такое функционирование системы, чтобы в каждый данный момент времени только одна структурная единица ПК пересылала данные по шине данных или осуществляла адресацию памяти.

К шине может быть подключено много приемных устройств. Сочетание управляющих и адресных сигналов определяет, для кого именно предназначаются данные на шине. Управляющая логика возбуждает специальные стробирующие сигналы, чтобы указать получателю, когда ему следует принимать данные.

Управляющая логика активизирует в каждый конкретный момент только одно устройство, которое становиться ведущим. Когда устройство активизировано, оно помещает свои данные на шину. Все другие микросхемы в этот промежуток времени должны блокироваться с помощью соответствующего сигнала на линии управления.

Цикл шины

Микропроцессор взаимодействует с внешней средой с помощью шины адреса/данных/состояния и нескольких управляющих сигналов. Собственно взаимодействие заключается в выполнении одной из двух операций: МП либо выводит (записывает) данные, либо вводит (считывает) данные или команды. В каждой из этих операций процессор должен указывать то устройство, с которым он будет взаимодействовать; другими словами, процессор должен адресовать ячейку памяти либо порт ввода или вывода.

Собственно взаимодействие заключается в выполнении одной из двух операций: МП либо выводит (записывает) данные, либо вводит (считывает) данные или команды. В каждой из этих операций процессор должен указывать то устройство, с которым он будет взаимодействовать; другими словами, процессор должен адресовать ячейку памяти либо порт ввода или вывода.

Для передачи данных или выборки команды процессор инициирует так называемый цикл шины. Кроме процессора, цикл шины могут инициировать и другие устройства, например, арифметический сопроцессор.

Цикл шины представляет собой последовательность событий, в течение которой процессор выдает адрес ячейки памяти или периферийного устройства, а затем формирует сигнал записи или считывания, а также выдает данные в операции записи. Выбранное устройство воспринимает данные с шины в цикле записи или помещает данные на шину в цикле считывания. По окончании цикла шины устройство фиксирует записываемые данные или снимает считываемые данные.

Рассмотрим цикл шины микропроцессора 8086, который имеет совмещенную 20-разрядную шину адреса/данных/состояния и шину управления (рис. 4).

4).

Рис. 4. Шины микропроцессора 8086

Цикл шины микропроцессора 8086 состоит минимум из четырех тактов синхронизации, называемых также состояниями T, которые идентифицируются спадающим фронтом сигнала синхронизации CLC. В первом такте (T1) процессор выдает на шину адреса/данных/состояния AD20-AD0 адрес устройства, которое будет источником или получателем информации в текущем цикле шины. Во втором такте (T2) процессор снимает адрес с шины и либо переводит тристабильные буферы линий AD15-AD0 в высокоимпедансное состояние, подготавливая их к выводу информации в цикле считывания, либо выдает на них данные в цикле записи.

Управляющие сигналы, инициирующие считывание, запись или подтверждение прерываний, всегда выдаются в такте T2. В максимальной конфигурации системы сигнал записи формируется в такте T3, чтобы гарантировать стабилизацию сигналов данных до начала действия этого сигнала.

В такте T2 старшие четыре линии адреса/состояния переключаются с режима выдачи адреса на режим выдачи состояния. Сигналы состояния предназначены в основном для диагностических целей, например, идентифицируют сегментный регистр, который участвует в формировании адреса памяти.

Сигналы состояния предназначены в основном для диагностических целей, например, идентифицируют сегментный регистр, который участвует в формировании адреса памяти.

В течение такта T3 процессор сохраняет информацию на линиях состояния. На шине данных в цикле записи сохраняются выводимые данные, а в цикле считывания производится опрос вводимых данных.

Тактом T4 заканчивается цикл шины. В этом такте снимаются все управляющие сигналы и выбранное устройство отключается от шины.

Таким образом, цикл шины для памяти или периферийного устройства представляет собой асинхронное действие. Устройство может управлять циклом шины только путем введения состояний ожидания.

Процессор выполняет цикл шины в том случае, когда ему необходимо осуществить запись или считывание информации. Если циклы шины не требуются, шинный интерфейс реализует холостые состояния Ti, в течение которых процессор сохраняет на линиях состояния сигналы состояния от предыдущего цикла шины.

Статьи к прочтению:

- Штрих-кодовая татуировка теперь требуется по закону

- Симметричная многопроцессорная архитектура smp

Как выбрать видеокарту.

Или почему шина 256 бит — не рулит. (см. описание)

Или почему шина 256 бит — не рулит. (см. описание)

Похожие статьи:

Интерфейсная шина i2c. назначение, форматы передачи данных, основные технические характеристики

Современные устройства радиоэлектронной техники используют большое число микросхем, что требует много линий для адресации, выбора и управления их…

Шины микропроцессорной системы

Шины микропроцессорной системы и циклы обмена Самое главное, что должен знать разработчик микропроцессорных систем — это принципы организации обмена…

Шина управления — Студопедия

Поделись

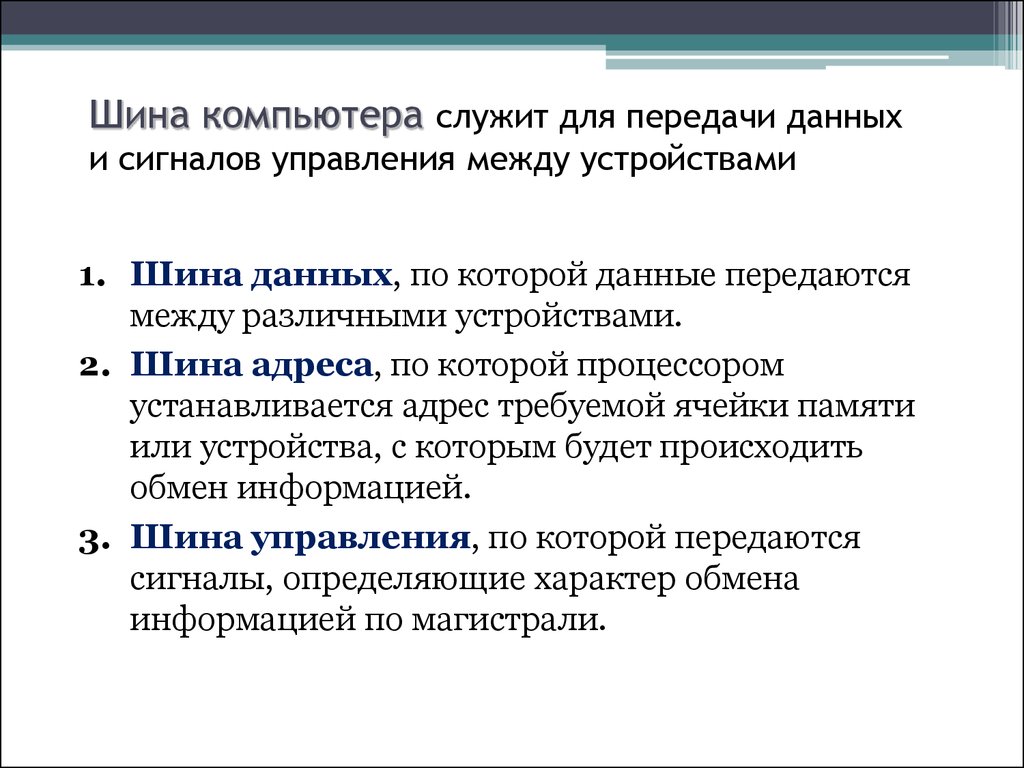

Шина данных,

Шина адресная,

ШИНЫ

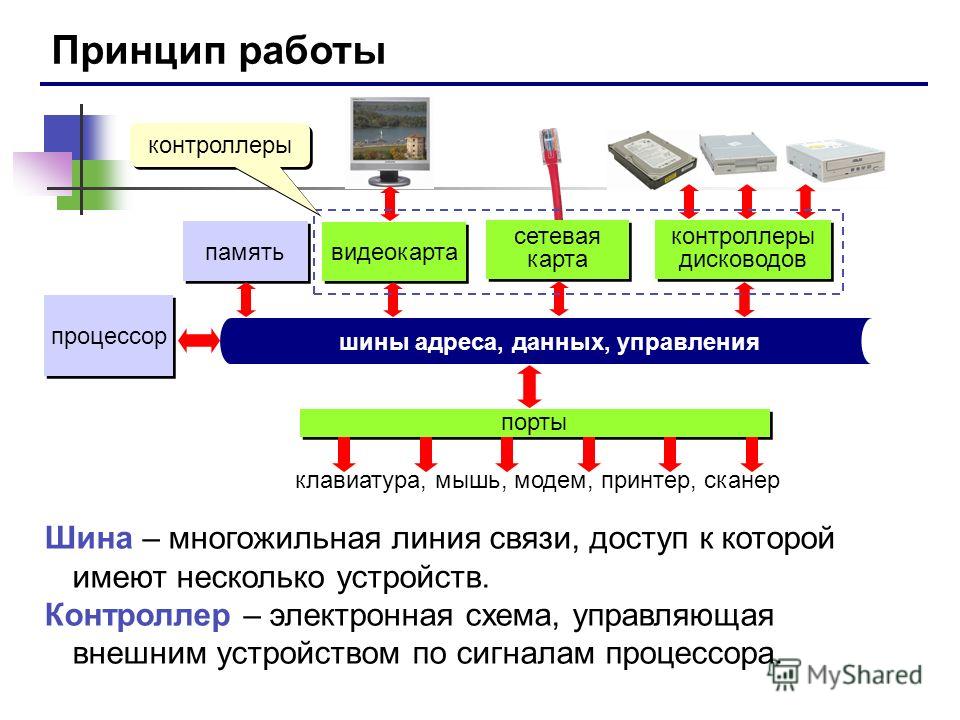

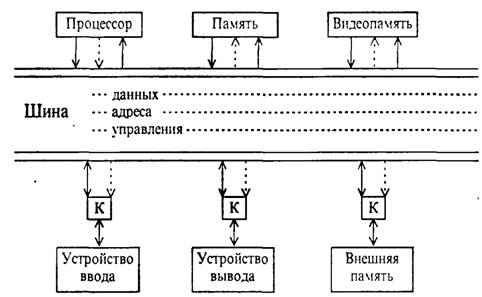

Шины данных и шины адресов (на физическом уровне) – многопроводные линии с гнездами для подключения электронных схем.

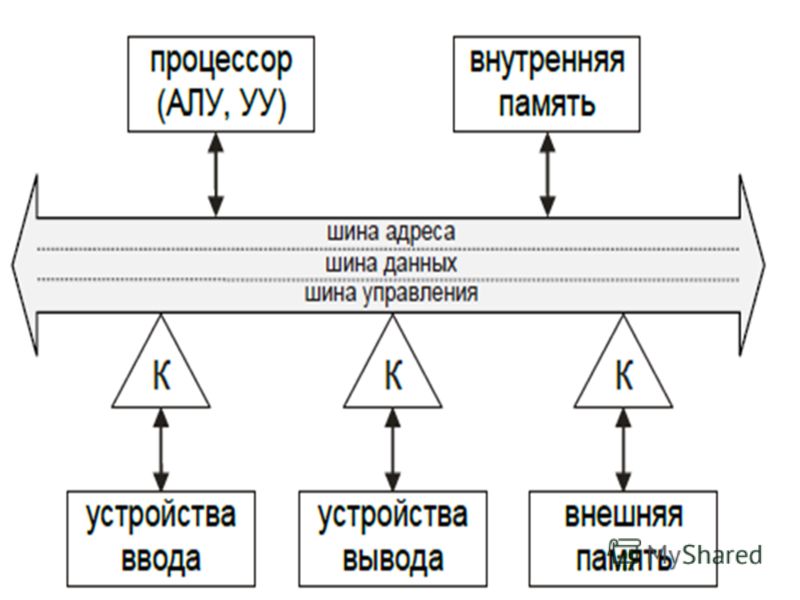

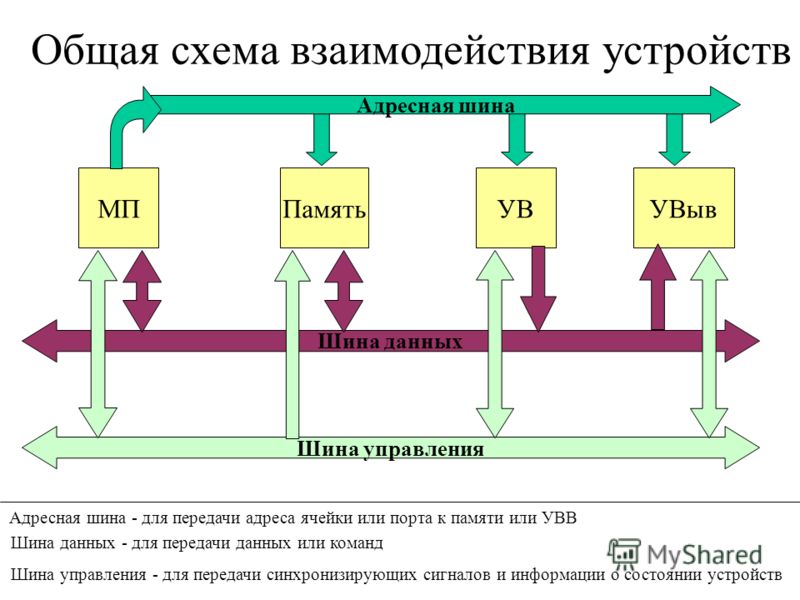

Совокупность проводов магистрали разделяется на отдельные группы: шину адреса, шины данных и шину управления:

Шина адреса предназначена для передачи адреса того устройства (или той ячейки памяти), к которому обращается процессор.

По шине данных передаётся вся информация при записи и считывании.

По шине управления передается управляющий сигнал и сигналы синхронизации.

Процесс взаимодействия процессора и памяти сводится к двум операциям – записи и считывания информации. При записи процессор по специальным проводникам (шина адреса) передает биты, кодирующие адрес, по другим проводникам – управляющий сигнал «запись», и еще по другой группе проводников (шины данных) передает записываемую информацию.

При чтении по шине адреса передается соответствующий адрес оперативной памяти (ОП), а с шины данных считывается нужная информация.

По шине адресов передается также адрес порта ввода — вывода, который нужен для

использования ЦП. Сигнал ввода-вывода определяет направление передачи.

Шины могут соединять ЦП как с памятью, так и с УВВ.

Современные компьютеры имеют прямую связь межу памятью и УВВ, что позволяет осуществлять передачу данных к периферийным устройствам и обратно без участия ЦП.

Этот метод передачи данных называется прямым доступом к памяти (ПДП).

Преимуществом ПДП является то, что скорость передачи обеспечивается только временем доступа к памяти (обычно менее 1 мкс).

Для передачи данных через ЦП требуется несколько команд, и на это уходит в 10-20 раз больше времени.

Прямой доступ к памяти применяется с быстродействующими периферийными устройствами, такими как магнитные диски, быстродействующие линии связи или дисплеи.

1.4 ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

это основной рабочий компонент компьютера, который:

— выполняет арифметические и логические вычисления;

— управляет вычислительным процессом;

— координирует работу всех устройств компьютера.

ЦП обрабатывает данные. Он выбирает команды из памяти, дешифрирует их и выполняет.

ЦП вырабатывает временные сигналы и сигналы управления, передает в память и из памяти и устройств ввода-вывода, выполняет арифметические и логические операции и идентифицирует внешние сигналы.

На рис.1.1.4. показан структура типичного ЦП.

Рис.1.1.4.

В течение каждого цикла командыЦП выполняет много управляющих функций:

1. помещает адрес команды в адресную шину памяти;

2. получает команду из шины ввода данных и дешифрирует ее;

3. выбирает адреса и данные, содержащиеся в команде; адреса и данные могут находиться в памяти или в регистрах;

4. выполняет операцию, определенную в коде команды. Операцией может быть арифметическая или логическая функция, передача данных или функция управления;

5. следит за управляющими сигналами, такими как прерывание, и реагирует соответствующим образом;

6. генерирует сигналы состояния, управления и времени, которые необходимы для нормальной работы УВВ и памяти.

Таким образом, ЦП является “мозгом”, определяющим действия компьютера.

шина данных, адреса и управления

Скотт Торнтон

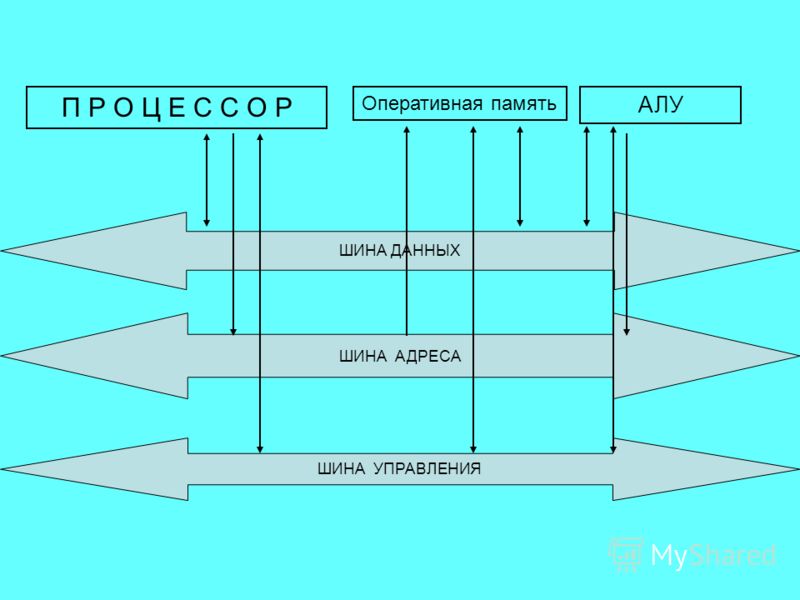

Шина — это канал, по которому цифровые сигналы быстро перемещают данные. С процессорами связаны три внутренние шины: шина данных, шина адреса и шина управления. Вместе эти три составляют «системную шину». Системная шина — это внутренняя шина, предназначенная для соединения процессора с внутренними аппаратными устройствами, ее также называют «локальной» шиной, Front Side Bus или иногда в общих чертах называют «шиной памяти».

С процессорами связаны три внутренние шины: шина данных, шина адреса и шина управления. Вместе эти три составляют «системную шину». Системная шина — это внутренняя шина, предназначенная для соединения процессора с внутренними аппаратными устройствами, ее также называют «локальной» шиной, Front Side Bus или иногда в общих чертах называют «шиной памяти».

Данные, входящие и исходящие из шины данных, являются двунаправленными, поскольку процессор считывает и записывает данные, однако остальные являются однонаправленными, поскольку процессор всегда определяет, когда и что он будет читать или записывать. Адресная шина передает сигналы адресации от процессора к памяти, устройствам ввода-вывода (или периферийным устройствам) и другим адресуемым устройствам вокруг процессора. Сигналы управления выходят из процессора, но не входят в него.

Рисунок 1: Внутренняя системная шина. Автор В. Новицки. Собственная работа, основанная на диаграмме из книги «Основы компьютерной организации и архитектуры» Линды Нулл и Юлии Лобур. СС BY-SA 3.0

СС BY-SA 3.0

«Ширина» шины данных MCU обычно составляет 8, 16, 32 или 64 бита, хотя возможны MCU только с 4-битной шиной данных или шириной более 64 бит. Ширина шины данных отражает максимальное количество данных, которое может быть обработано и доставлено за один раз. 64-разрядный процессор имеет 64-разрядную шину данных и может одновременно передавать 64-разрядные данные, а чтение или запись данных определяется шиной управления. Физическое расположение данных в памяти передается по адресной шине. Внутренний аппаратный компонент, получив адрес от адресной шины и собираясь получить данные, включает буфер, чтобы разрешить поток сигналов в или из места, которое было назначено адресной шиной. Адресная шина несет только информацию об адресе и синхронизируется с шиной данных для выполнения задач чтения/записи от процессора. Адресная шина настолько широка, насколько это необходимо для адресации всей памяти в системе.

Другие коммуникационные шины также взаимодействуют с процессором, но являются внешними по отношению к системе, например универсальная последовательная шина, RS-232, сеть контроллеров (CAN), eSATA и другие. Внешние периферийные устройства могут быть настроены для использования внутренней шины, и это было обычным делом для компьютеров, которые использовали «карты расширения» для подключения продуктов к внутренней шине. Однако с одной картой на устройство это стало неприемлемым в долгосрочной перспективе, и были разработаны другие системы связи по шине, такие как USB.

Внешние периферийные устройства могут быть настроены для использования внутренней шины, и это было обычным делом для компьютеров, которые использовали «карты расширения» для подключения продуктов к внутренней шине. Однако с одной картой на устройство это стало неприемлемым в долгосрочной перспективе, и были разработаны другие системы связи по шине, такие как USB.

Системная шина может быть «расширена» для связи с другими компьютерами через шасси, называемое объединительной платой. Внутренние шины имеют очень высокую пропускную способность и низкую задержку. Несколько компьютеров могут быть установлены в стойку на одной объединительной плате для очень быстрой связи между компьютерами.

Рубрики: 16-разрядные, 32-разрядные, 64-разрядные, 8-разрядные, Часто задаваемые вопросы, Рекомендуемые, Эксперты отрасли, микроконтроллер, Продукты с тегами: основы, Часто задаваемые вопросы

6.2: Процессор — шина

- Последнее обновление

- Сохранить как PDF

- Идентификатор страницы

- 82864

- Патрик МакКланахан

- Колледж Сан-Хоакин Дельта

Шина управления

В компьютерной архитектуре шина управления является частью системной шины, используемой ЦП для связи с другими устройствами внутри компьютера. В то время как адресная шина несет информацию об устройстве, с которым взаимодействует ЦП, а шина данных передает фактические обрабатываемые данные, шина управления передает команды от ЦП и возвращает сигналы состояния от устройств. Например, если данные считываются или записываются на устройство, соответствующая линия (чтение или запись) будет активной (логическая единица).

В то время как адресная шина несет информацию об устройстве, с которым взаимодействует ЦП, а шина данных передает фактические обрабатываемые данные, шина управления передает команды от ЦП и возвращает сигналы состояния от устройств. Например, если данные считываются или записываются на устройство, соответствующая линия (чтение или запись) будет активной (логическая единица).

Адресная шина

Адресная шина — это шина, которая используется для указания физического адреса. Когда процессору или устройству с поддержкой DMA необходимо прочитать или записать ячейку памяти, он указывает эту ячейку памяти на адресной шине (значение, которое нужно прочитать или записать, отправляется по шине данных). Ширина адресной шины определяет объем памяти, которую система может адресовать. Например, система с 32-битной адресной шиной может адресовать 232 (4 294 967 296) ячеек памяти. Если каждая ячейка памяти содержит один байт, адресное пространство памяти составляет 4 ГБ.

Шина данных/памяти

Шина памяти — это компьютерная шина, которая соединяет основную память с контроллером памяти в компьютерных системах. Первоначально использовались шины общего назначения, такие как VMEbus и шина S-100, но для уменьшения задержки современные шины памяти предназначены для прямого подключения к микросхемам DRAM и, таким образом, разработаны органами по стандартизации микросхем, такими как JEDEC. Примерами являются различные поколения SDRAM и последовательные двухточечные шины, такие как SLDRAM и RDRAM. Исключением является модуль DIMM с полной буферизацией, который, несмотря на то, что он был тщательно разработан для минимизации эффекта, подвергался критике за более высокую задержку.

Первоначально использовались шины общего назначения, такие как VMEbus и шина S-100, но для уменьшения задержки современные шины памяти предназначены для прямого подключения к микросхемам DRAM и, таким образом, разработаны органами по стандартизации микросхем, такими как JEDEC. Примерами являются различные поколения SDRAM и последовательные двухточечные шины, такие как SLDRAM и RDRAM. Исключением является модуль DIMM с полной буферизацией, который, несмотря на то, что он был тщательно разработан для минимизации эффекта, подвергался критике за более высокую задержку.

Адаптировано из:

«Шина (вычисления)» нескольких участников, Википедия лицензируется в соответствии с CC BY-SA 3.0

«Шина памяти» несколькими участниками, Википедия лицензируется в соответствии с CC BY-SA 3.0

«Шина управления» несколькими участниками Авторы, Википедия находится под лицензией CC BY-SA 3.0

.

Эта страница под заголовком 6.2: The Processor — Bus распространяется по лицензии CC BY-SA, ее автором, ремиксом и/или куратором является Патрик МакКланахан.